## PARK III

up-to-date electronics for lab and leisure

CCIR standard TV test pattern generator

darkroom timer with logarithmic scale

FM mains intercom ystem with abyphone' extension

Editor : W. van der Horst

Deputy editor

: P. Holmes

Technical editors: J. Barendrecht

G.H.K. Dam

E. Krempelsauer G.H. Nachbar

A. Nachtmann Fr. Scheel

K.S.M. Walraven

Art editor

: C. Sinke

Subscriptions

: Mrs. A. van Meyel

U.K. editorial offices, administration and advertising: Elektor Publishers Ltd., Elektor House, 10 Longport Street, Canterbury CT1 1PE, Kent, U.K. Tel.: Canterbury (0227)-54430. Telex: 965504. Please make all cheques payable to Elektor Publishers Ltd.

at the above address. Bank: 1. Midland Bank Ltd., Canterbury, A/C no. 11014587,

Sorting code 40-16-11, Giro no. 3154254. 2. U.S.A. and Canada: c/o World Way Postal Center P.O. Box 80689, Los Angeles, Cal. 90080, A/C no. 12350-04207.

Assistant Manager and Advertising : R.G. Knapp Editorial : T. Emmens

Elektor is published monthly on the third friday of each month.

1. U.K. and all countries except the U.S.A. and Cananda: Cover price £ 0.45.

Number 27/28 (July/August), is a double issue, 'Summer Circuits', price £ 0.90.

Single copies (incl. back issues) are available by post from our Canterbury office, at £ 0.60 (surface mail) or £ 0.95 (air mail). Subscriptions for 1977, January to December incl., £ 6.25 (surface mail) or £ 11.— (air mail).

Subscriptions from October to December 1977 £1.60 (surface mail)

2. For the U.S.A. and Canada.

Cover price \$ 1.50.

Number 27/28 (July/August), is a double issue, 'Summer Circuits', price \$ 3.-

Single copies (incl. back issues) \$ 1.50 (surface mail) or \$ 2.25 (air mail).

Subscriptions for 1977, January to December incl.,

\$ 18.— (surface mail) or \$ 27.— (air mail).

Subscriptions from October to December 1977 \$4.50 (surface mail). All prices include post & packing.

Change of address. Please allow at least six weeks for change of address, Include your old address, enclosing, if possible, an address label from a

Letters should be addressed to the department concerned: TQ = Technical Queries, ADV = Advertisements, SUB = Subscriptions; ADM = Administration; ED = Editorial (articles submitted for publication etc.); EPS = Elektor printed circuit board service. For technical queries, please enclose a stamped, addressed envelope.

The circuits published are for domestic use only. The submission of designs or articles to Elektor implies permission to the publishers to alter and translate the text and design, and to use the contents in other Elektor publications and activities. The publishers cannot guarantee to return any material submitted to them. All drawing, photographs, printed circuit boards and articles published in Elektor are copyright and may not be reproduced or imitated in whole or part without prior written permission of the publishers.

Patent protection may exist in respect of circuits, devices, components etc. described in this magazine.

The publishers do not accept responsibility for failing to identify such patent or other protection.

National advertising rates for the English edition of Elektor and/or international advertising rates for advertising at the same time in the English, Dutch and German issues are available on request.

Distribution: Spotlight Magazine Distributors Ltd. Spotlight House 1, Bentwell Road, Holloway, London N7 7AX.

Copyright © 1977 Elektor publishers Ltd - Canterbury.

Printed in the Netherlands.

What is a TUN? What is 10 n? What is the EPS service? What is the TQ service? What is a missing link?

Semiconductor types

Very often, a large number of equivalent semiconductors exist with different type numbers. For this reason, 'abbreviated' type numbers are used in Elektor wherever possible:

'741' stand for µA741, LM741, MC641, MIC741, RM741, SN72741, etc.

• 'TUP' or 'TUN' (Transistor, Universal, PNP or NPN respectively) stand for any low frequency silicon transistor that meets the following specifications:

| VOV    |

|--------|

| 00 mA  |

| 00     |

| 00 mW  |

| 00 MHz |

|        |

Some 'TUN's are: BC107, BC108 and BC109 families; 2N3856A, 2N3859, 2N3860, 2N3904, 2N3947, 2N4124. Some 'TUP's are: BC177 and BC178 families; BC179 family with the possible exeption of BC159 and BC179; 2N2412, 2N3251, 2N3906, 2N4126, 2N4291.

· 'DUS' or 'DUG' (Diode Universal, Silicon or Germanium respectively) stands for any diode that meets the following specifications:

|           | DUS   | DUG    |

|-----------|-------|--------|

| UR, max   | 25V   | 20V    |

| IF, max   | 100mA | 35mA   |

| IR, max   | 1µA   | 100 µA |

| Ptot, max | 250mW | 250mW  |

| CD, max   | 5pF   | 10pF   |

Some 'DUS's are: BA127, BA217, BA218, BA221, BA222, BA317, BA318, BAX13, BAY61, 1N914, 1N4148. Some 'DUG's are: OA85, OA91, OA95, AA116.

'BC107B', 'BC237B', 'BC547B' all refer to the same 'family' of almost identical better-quality silicon transistors. In general, any other member of the same

BC107 (-8, -9) families:

BC107 (-8, -9) ramines: BC107 (-8, -9), BC147 (-8, -9), BC207 (-8, -9), BC237 (-8, -9), BC317 (-8, -9), BC347 (-8, -9), BC547 (-8, -9), BC171 (-2, -3), BC182 (-3, -4), BC382 (-3, -4), BC437 (-8, -9), BC414

family can be used instead.

BC177 (-8, -9) families:

BC177 (-8, -9), BC157 (-8, -9), BC204 (-5, -6), BC307 (-8, -9), BC320 (-1, -2), BC350 (-1, -2), BC557 (-8, -9), BC251 (-2, -3), BC212 (-3, -4), BC512 (-3, -4), BC261 (-2, -3), BC416.

Resistor and capacitor values When giving component values, decimal points and large numbers of zeros are avoided wherever

possible. The decimal point is usually replaced by one of the

following abbreviations: (pico-) 10-12 p 10-9 n (nano-) = (micro-) = 10-6 ш

10-3 (milli-) = m (kilo-) 10<sup>3</sup> M (mega-) = 10<sup>6</sup>  $(giga-) = 10^9$ G

A few examples: Resistance value 2k7: 2700 Ω. Resistance value 470: 470  $\Omega$ .

Capacitance value 4p7: 4.7 pF, or 0.000 000 000 004 7 F Capacitance value 10n: this is the international way of writing 10,000 pF or .01 µF, since 1 n is 10<sup>-9</sup> farads or 1000 pF. Resistors are ¼ Watt 5% carbon types, unless otherwise specified. The DC working voltage of

capacitors (other than electrolytics) is normally assumed to be at least 60 V. As a rule of thumb, a safe value is usually approximately twice the DC supply voltage.

Test voltages

The DC test voltages shown are measured with a 20 kΩ/V instrument, unless otherwise specified.

U not V

The international letter symbol 'U' for voltage is often used instead of the ambiguous 'V'. 'V' is normally reserved for 'volts'. For instance:  $U_b = 10 \text{ V}$ , not  $V_b = 10 \text{ V}$ .

Mains voltages

No mains (power line) voltages are listed in Elektor circuits. It is assumed that our readers know what voltage is standard in their part of the world! Readers in countries that use 60 Hz should note that Elektor circuits are designed for 50 Hz operation. This will not normally be a problem; however, in cases where the mains frequency is used for synchronisation some modifi-

Technical services to readers e EPS service. Many Elektor articles include a lay-out for a printed circuit board. Some - but not all - of these boards are available ready-etched and predrilled. The 'EPS print service list' in the current issue always gives a com-

plete list of available boards.

cation may be required.

Technical queries. Members of the technical staff are available to answer technical queries (relating to articles published in Elektor) by telephone on Mondays from 14.00 to 16.30. Letters with technical queries should be addressed to: Dept. TQ. Please enclose a stamped, self addressed envelope; readers outside U.K. please enclose an IRC instead of stamps.

Missing link. Any important modifications to, additions to, improvements on or corrections in Elektor circuits are generally listed under the heading 'Missing Link' at the earliest opportunity.

## contents

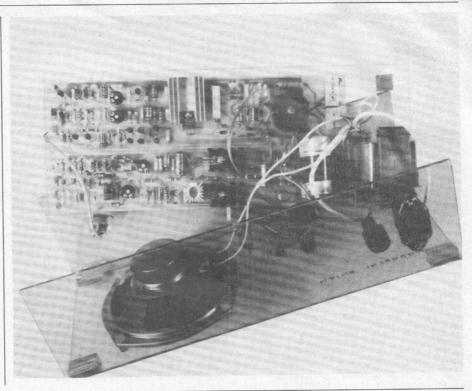

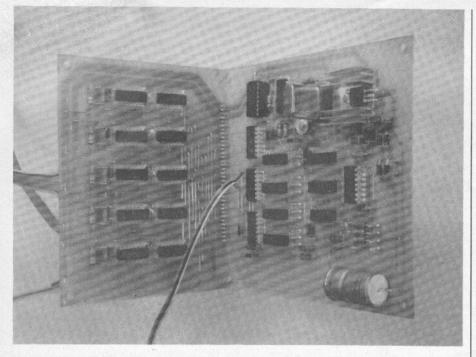

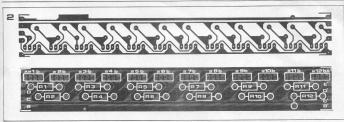

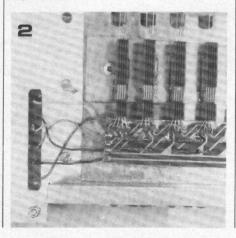

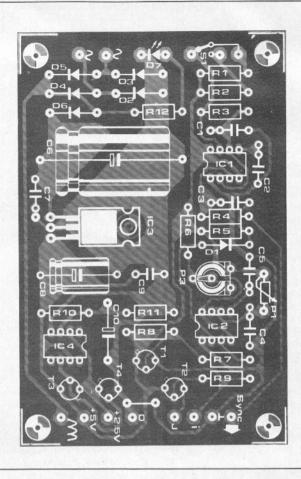

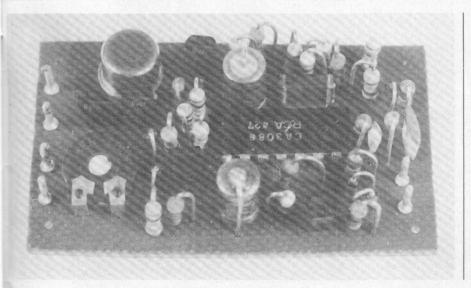

A complete station of the FM mains intercom consists of a transmitter, a receiver and a power supply. All three can be mounted on a single p.c.board.

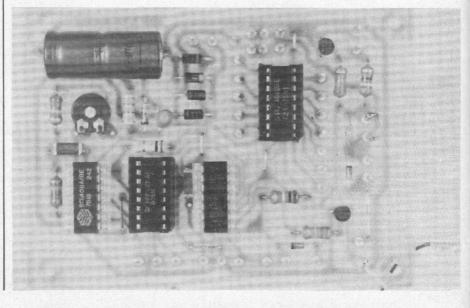

The control switches and indicator lights of the logarithmic darkroom timer are laid out in such a way that the unit should be easy to operate even when working in complete darkness.

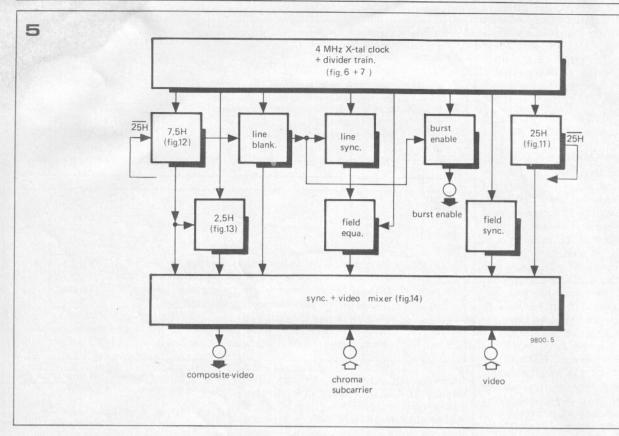

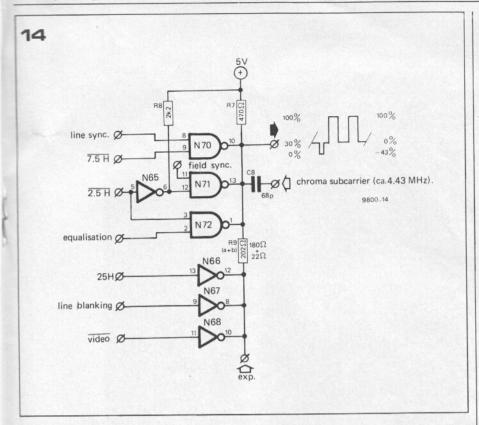

The line and field sync pulses produced by a television test generator must conform to a precisely defined international standard. The CCIR tv pattern generator uses a quartz oscillator and TTL divider stages to produce a video waveform that is well within the limits defined by the European CCIR.

The Japanese influence on electronics is becoming more and more widespread. An obvious further step in the right direction would be to paint the components in traditional oriental fashion, as illustrated by this month's cover . . .

| 0 | 0  |  |

|---|----|--|

| 4 | 10 |  |

| / | /  |  |

Volume 3 Number 9

. . . . . . 9-60

| selektor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9-12 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| introducing microprocessors (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9-16 |

| FM mains intercom                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9-18 |

| missing link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9-25 |

| working Perspex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9-26 |

| logarithmic darkroom timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9-28 |

| monitor switching for two tape decks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9-32 |

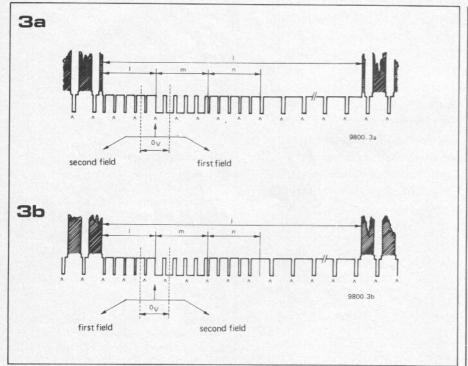

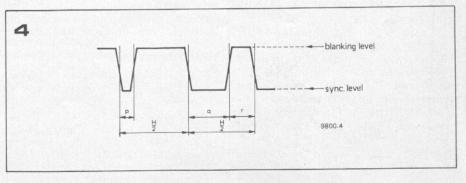

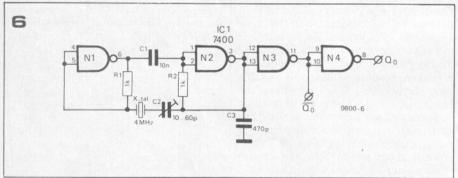

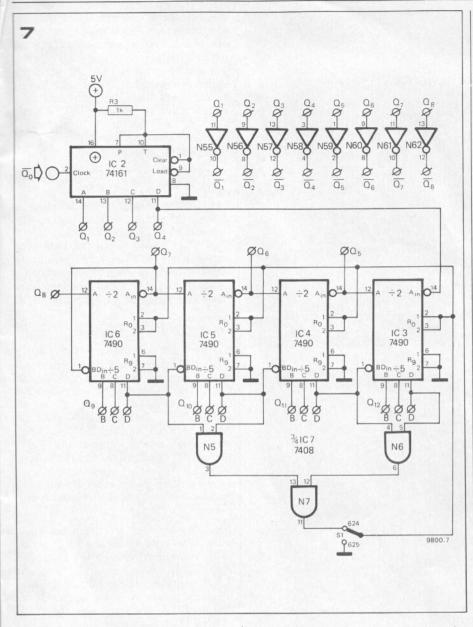

| CCIR tv pattern generator (1)  The basis of any television signal is a complex synchronisation waveform, which ensures that the scanning circuits of the TV receiver stay synchronised to the transmitted signal. Standards vary throughout the world, but in Europe the CCIR norm is used, and the basis of this design is a generator to provide a CCIR standard sync. signal. Of course, such a sync. signal is of very little use by itself, so the modular construction of the generator allows the addition of units to generate various video signals, the first of which is a test pattern generator giving a fully interlaced picture. | 9-33 |

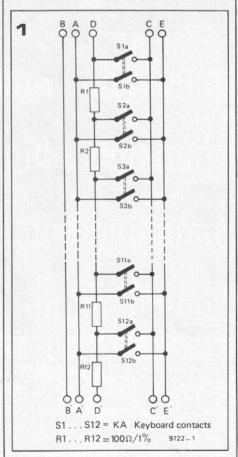

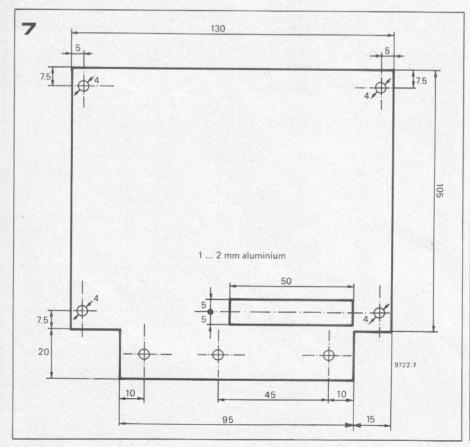

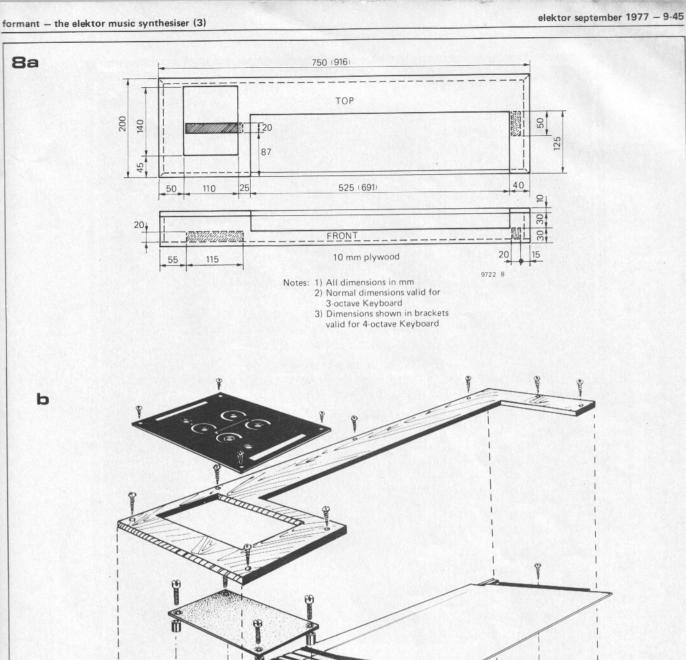

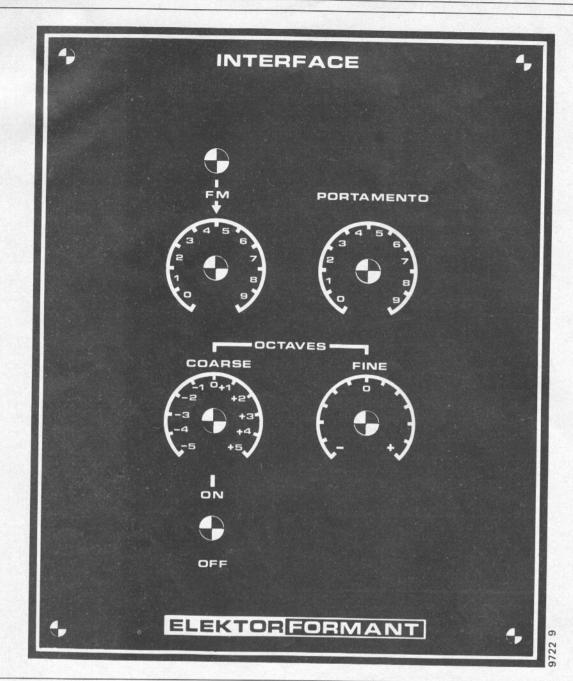

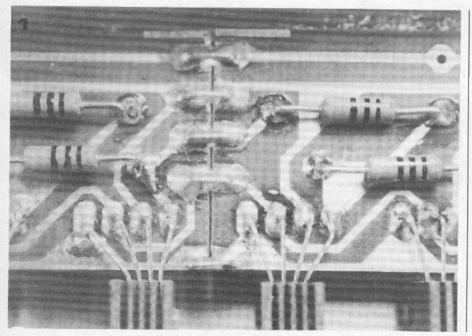

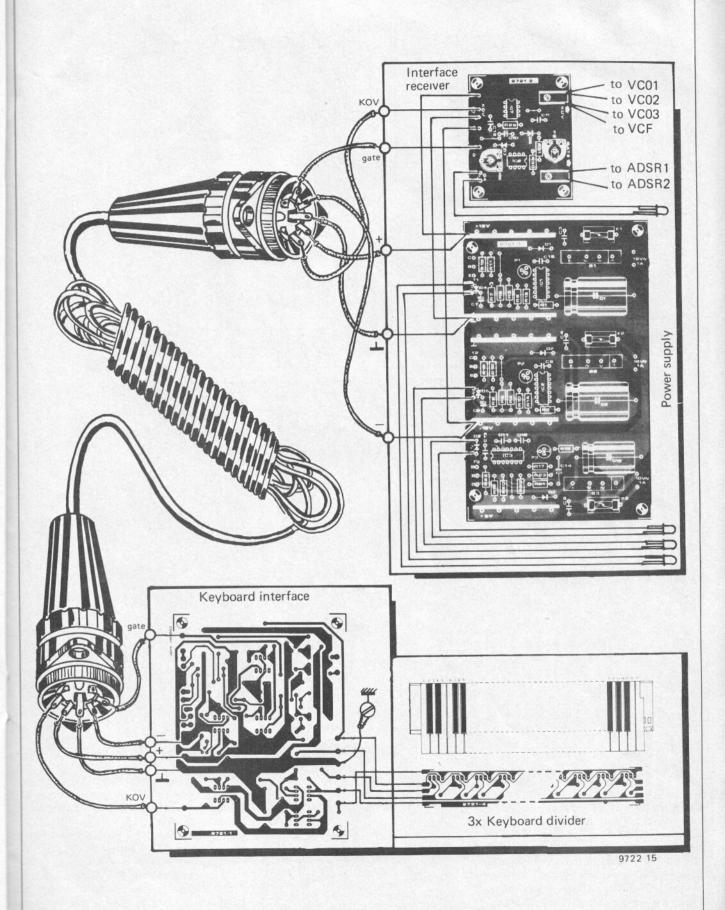

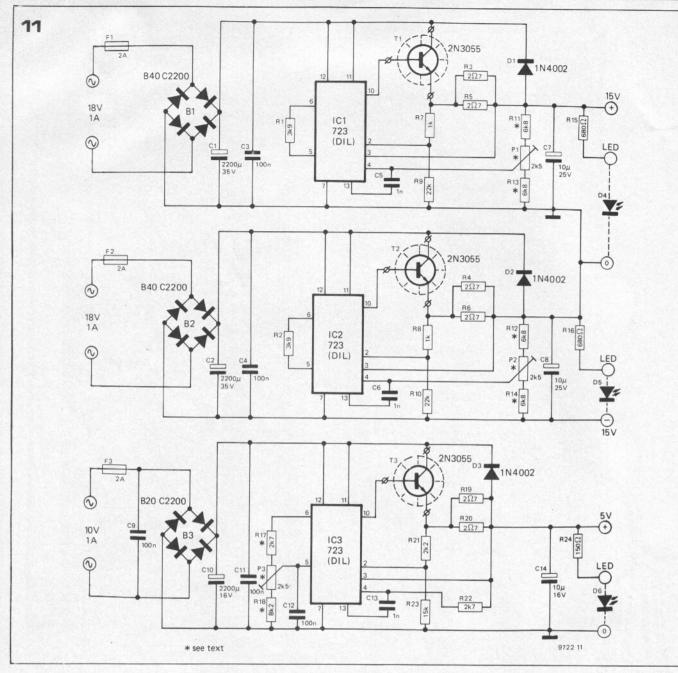

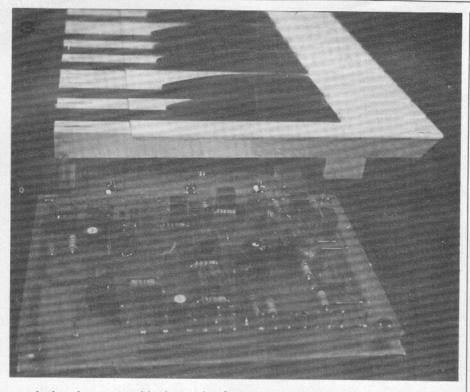

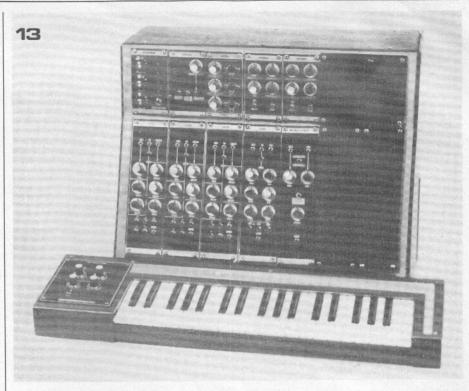

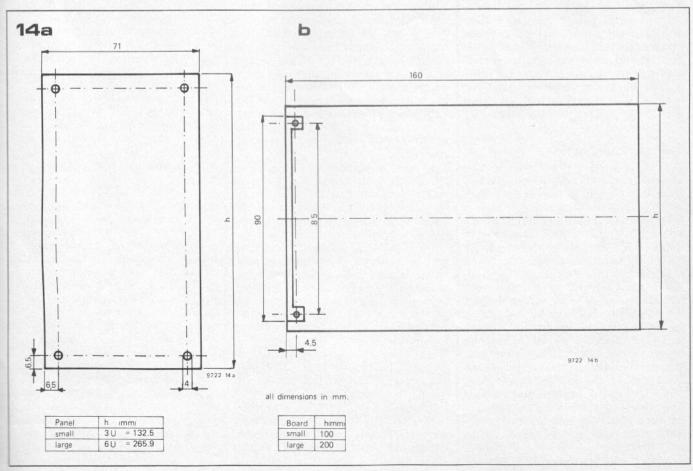

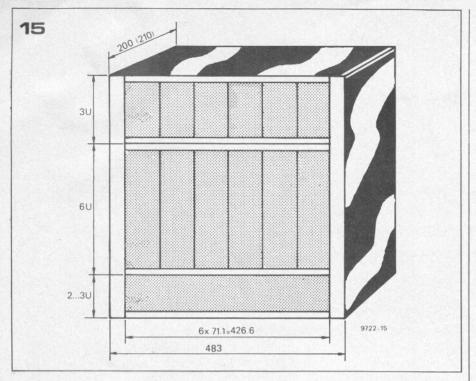

| Formant — the Elektor music synthesiser (3) C. Chapman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9-42 |

| In the previous article the keyboard and keyboard interface circuits were described, together with the printed circuit board for the keyboard interface. In this article the p.c. board layout for the keyboard resistance divider is given, together with constructional details of the keyboard case. The description of the voltage-controlled module unit is then commenced, starting with the power supply and details of the module case.                                                                                                                                                                                                 |      |

| coming soon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9-52 |

| Having described the servo amplifier in the previous article, the motor speed controller is discussed. This is followed by a description of the 'prop tester', which can be used to test servo amplifiers and motor controllers.                                                                                                                                                                                                                                                                                                                                                                                                                |      |

## Where are those buses?

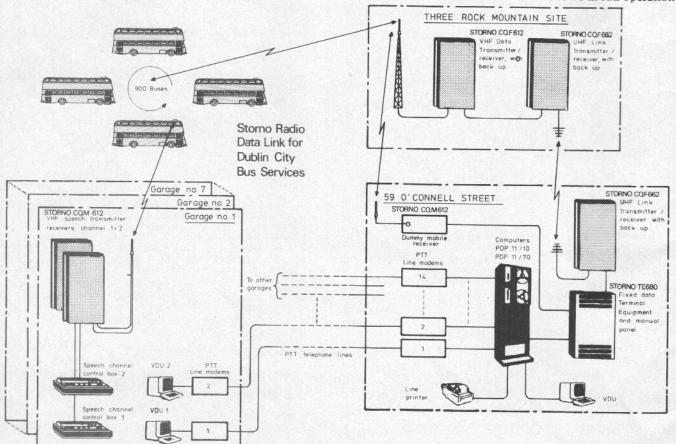

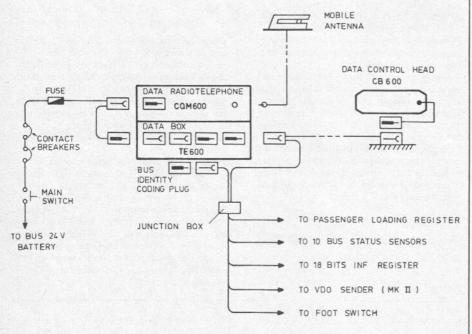

Coras Iompair Eireann (CIE), Ireland's national transport company, are installing a fully automatic vehicle monitoring (AVM) system for Dublin City Bus Services' entire fleet of some 900 buses which carry over-216 million passengers and operate over 32 million miles each year.

Storno Limited of Camberley, Surrey are the main suppliers for the system which will enable the entire fleet to be monitored by Control Inspectors from seven garages. The system is based on a dual computer arrangement which automatically collects location data from each bus on a route. The results are presented on visual display units (VDU's) so that Control Inspectors in each garage can see at a glance the actual, and scheduled, position on all buses on a particular route.

Although the collection of location data is automatic, and does not require the driver to answer queries, normal speech contact between driver and Control Inspector is also provided in this complete radio communications system. This system will enable CIE to provide improved services for passengers by reducing bus waiting times, operating services on time, and by having the facility to summon aid in cases of emergency, or passenger illness. Significant benefits are also being provided for the CIE management and 4,000 workforce. Of the utmost importance, the system generates valuable statistical information which is available within 24 hours and forms the basis of a comprehensive management information service for the scheduling, maintenance and operating departments.

The Control Inspectors, who are now being removed from often unpleasant outdoor work, are achieving a re-newed sense of job satisfaction and involvement from being able to control a full bus route, or group of routes without assistance, or interference.

Improved morale has been achieved for the operating staff who will now be responsible to a single Control Inspector instead of reporting to several Control Inspectors located at different parts of their route. The greater control achieved with radio is providing an equalisation of workload between crews, enabling them to take their mealbreaks at correct times, and providing immediate assistance in the event of assault, or vandalism.

Dublin Bus Services first started experimenting with radio telephones in 1970. Tests proved so satisfactory that there are now 740 radio equipped buses in service using 14 voice channels. Due to the limited availability of VHF channels, expansion to the remainder of the fleet could only be achieved through higher utilisation of existing allocation, and the solution appeared to lie in the automation of the existing scheme. Major trials took place in 1975 on all aspects of automatic vehicle monitoring on 100 buses from the Phibsborough garage. The buses were fitted with Stornophone CQM612 semi-duplex VHF FM mobile radio telephones, designed to facilitate data transmission. A telemetry unit stored the data message and facilitated transmission when interrogated by the computer located at the CIE headquarters in O'Connell Street, Results were presented on two VDU's at the Phibsborough garage. A printer provided hard copies of specific information.

The data link comprised a base station at the computer site, and a station at Three Rock Mountain, approximately seven miles away to relay the information from the computer to the mobile bus units and vice versa. These comprehensive tests included location accuracy, facilities tests, tests on voice communications, computer system and display responses, equipment reliability, Control Inspectors' and operatives' reactions. The results obtained paved the way for the complete AVM system now being installed and due to be in full operation

by mid 1979.

When fully operational a 'front end' PDP 11/10 computer will interrogate each bus in turn at the rate of 900 buses/ minute via a fully duplicated radio system. It will also handle requests to speak. Once verified the bus replies are fed into a larger PDP 11/70 machine which presents the results as actual and scheduled positions of the buses on individual routes on 2000 character screen VDU's — a number of which with a printer are being located at each of the seven garages.

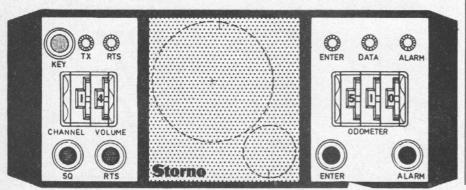

This will enable Control Inspectors in each garage to see at a glance the positions of all buses on a particular route so that they get an accurate picture of the situation as it is, and as it should be, to allow them to accurately make any changes that may be necessary to maintain, or improve services. Additionally, as part of the improvement of control techniques a number of closed circuit television cameras (CCTV's) are being installed at city centre points. These will provide Control Inspectors with an awareness of traffic conditions and build-up of passenger queues. Route Control Inspectors can operate the CCTV's which incorporate low light level lenses for night operation together with pan, tilt, zoom and focus facilities. The bus radio is being modified to accept and transmit the computer data and this, together with a bus data unit and control head comprises the bus

equipment. The control head provides the means of establishing voice communications between the driver and the Control Inspector and also feeding in the odometer reading at commencement of each journey to identify its precise location. Thereafter, location identification is automatic as the odometer is fitted to the final drive in parallel with the normal speedometer drive unit and generates pulses to the data unit at 44 yard intervals. The control head also incorporates an input for emergencies. The computer can also make direct inputs to the odometer.

The bus data unit stores the location of the bus and passenger loading. It also incorporates facilities to record up to

The Storno bus data control head provides the means of feeding in the three-digit code odometer reading at commencement of each journey to identify the precise location of the bus. Thereafter, location identification is automatic. When the driver wishes to speak he uses the RTS button which informs the Control Inspector through a VDU of his request. Up to eight such requests may be displayed at any one time.

Every 20 seconds a general call is sent to all Storno bus data units searching for an 'alarm' condition. Should any bus have its 'alarm' button depressed it will respond by causing its number and location to flash continuously on the Control Inspectors VDU. At the same time the computer automatically switches the bus to the speech mode thus giving drivers speech contact with their respective Control Inspectors on average within ten seconds of pressing the 'alarm' button.

Close-up of typical map shown on the VDU's and up-dated automatically at least every two minutes. The route is shown as two horizontal lines — one for each direction of travel. The scheduled positions for the buses operating on the route are shown on the inside of the diagram. Actual positions are plotted on the outside of the diagram and are represented by the duty number of the bus concerned.

deemed to be under the first character of the duty number. Time and route numbers are shown on the first line of the screen. Driver 'alarm' calls are flashed on and off on the first line until answered by the Control Inspectors. Requests to speak by bus crews appear on the last line and again will remain there until cleared by the Control Inspectors. Columns on the right-hand side of the screen give additional information on buses being monitored.

| TIME 10:58  |        | )5 -APR-7                               | 7      |        | AL    | ARM10/19 | CHECK 40/01 |       |       |

|-------------|--------|-----------------------------------------|--------|--------|-------|----------|-------------|-------|-------|

|             |        |                                         |        | OFX    |       |          |             | SET ( |       |

|             |        |                                         |        | 15A    |       |          |             | 1015  | 0411  |

|             |        |                                         |        | 07A    |       |          |             | 4005  | 1003  |

|             |        |                                         |        | 18     |       |          |             |       |       |

| 06V         | 14A    | 24                                      | 21A    | 16V    |       |          |             |       |       |

|             |        |                                         |        |        |       |          | ++          | GARA  | 3E    |

| 06- 14/     | 4-     | 24                                      |        | 21A#   | 16+   | 18       | 08-         | 0410  | 4011  |

|             | 17     |                                         |        |        |       | 07A+     |             | 1009  | 102   |

|             |        | SHLRD                                   |        | STGRN  |       |          |             |       |       |

| BELFD       | DBRCH  |                                         | WATRO  |        | OCOST | STPET    | PHXPK       |       |       |

|             |        |                                         | 22+    |        |       |          | 4.          |       | EPLY  |

| 01A         | 19:    | 1 13                                    | A#     | 04     | 11A   | 03.      | 15A         | 15    | 20 06 |

|             |        |                                         |        |        |       |          |             |       |       |

|             | 01/    | A                                       | 13A    | 22 04V | 1     | 1A       |             |       |       |

|             | 15     | 9                                       |        |        |       |          |             |       |       |

|             |        |                                         |        |        |       |          |             | INVA  | LID   |

|             |        |                                         |        |        |       |          |             | 01    | 18 16 |

|             |        |                                         |        |        |       |          |             | 13    | 22 0  |

| OVERFLOW: X | 03 09  | A 08 17                                 |        |        |       |          |             |       |       |

| 0. L LOW. X | 00,000 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |        |        |       |          |             |       |       |

| COMMAND?    |        | COMMAN                                  | D LINE |        |       |          |             |       |       |

|             |        | PRINTE                                  |        |        |       |          |             |       |       |

|             |        |                                         |        |        |       |          |             |       |       |

ten different mechanical and operating features, such as, excessive engine temperature and oil pressure. It also checks all incoming messages and controls the radio from receive to transmit.

The data link is similar to the one used in the 1975 trials, and again comprises a data base at the central computer site, and a relay station on Three Rock Mountain. The link is in two parts

-a VHF link between the relay station and the mobile unit, and a UHF link between the relay station and the central computer site.

The VHF equipment consists of a Stornophone CQF612 FM duplex base station giving 25 watts RF output. It operates on a 25 kHz channel spacing and is modified to permit the transmission of data signals.

The relay station transmitter outputs to an omnidirectional antenna and the receiver outputs to the adjacent UHF unit. The UHF link comprises two CQF662 duplex base stations — one on Three Rock Mountain and the other in O'Connell Street. The RF output is one watt and is fed into a directional antenna.

The data base station and data link are duplicated throughout and the standby link may be selected remotely from the O'Connell Street headquarters or from a garage based VDU.

The improved radio communications being introduced are helping to provide a reasonable level of public transport service under difficult congested operating conditions.

## bus radio/data box installation layout

LOUDSPEAKER

## Inventions

The current Jubilee Year passion for discovering the best of British inventions and techniques is to be given an unique audience in November that will provide United Kingdom ingenuity and technology with its biggest-ever world boost: the Sixth International Exhibition of Inventions in Geneva from 25 November to 4 December 1977. This Swiss Government-backed exhibition is the world's leading inventors' showplace where more than 1,000 new ideas and developments will be exhibited from 26 countries and where last year 350 licences were negotiated and exhibitors did £5-million worth of business during the 10-day exposition. There are 22 classes of exhibits, from general mechanical engineering through clothing and footwear to games and toys. An international jury representing 10 nations awards prizes from Grand Prix to bronze medals, visitors vote an Oscar award, the world Press presents its own prize, there are special awards for environment, transport, clock and watch-making, for the best foreign invention and prizes from the French, Spanish and Dutch Chambers of Commerce for their best national invention The reputation of the Geneva exhibition

is now so high that it attracts more

exhibits than all other international inventors' exhibitions put together. But exhibitions in general, and international events in particular, have the limiting disadvantage of cost. Twometres all round stand space will cost at least £200. Carpets, furniture and decorations another £150. International Commercial Network of Harrowgate now offer a unique solution to this problem. They have arranged a special British inventions show stand where they will display a group of special television-type monitor screens on which will be shown a series of threeminute colour films of each British invention or new development. These films will be accompanied by sound commentary in English, French, German and Italian. Visitors can select the invention they wish to see and choose the language of commentary. Inventors and companies may provide their own already-made Super-8 or 8 mm three-minute colour films with English commentary either on tape or script. Translated recordings will then be made at no charge. If there is no film this will be produced by Inter-View Productions. The cost of taking a film that already exists to Geneva and representing the British interests at the 10-day show is around £200. If a film is specially produced the total cost will be under £500, perhaps much less if film demands are simple.

(203 S)

## Optical waveguides used in Air Force's data-carrying cable

Optical waveguides made by Corning are an essential part of a cable installed at the U.S. Air Force Arnold Engineering Development Center in Tennessee.

The glass waveguides are contained in a custom-made cable of the General Cable Corporation that connects rocket engine test sites with a central data processing facility.

The cable contains six waveguides, along with several copper conductors. Each waveguide may be employed independently for transmitting, at high-speed, data signals or any other information, including voice and video signals.

The waveguides transmit data from the engine test sites to the base computer center, located approximately two kilometers away.

The optical waveguides were chosen for the installation because of their large data-carrying capability, and because they are immune to hostile environments, particularly electromagnetic interference.

Measuring about 0.005-inch (0.127 mm) in diameter, or about the thickness of a human hair, the waveguides are well protected by other cable components. Because the cable is buried for most of its 7,000-foot (2,100-meter) length, special steps were taken to make it suitable for such an environment. The cable consists of a welded tubular aluminium sheath surrounding the fibers and their support structure, a polyethylene inner jacket, a corrugated steel wrapping and a polyethylene outer jacket. The cable is suitable for installation in ducts or can be buried directly in the ground.

The installation at the Arnold Center is particularly significant because it is intended as an operational system, not an experimental one. The complete system is expected to be in service by mid-1977, when installation of other elements of the system is complete. The graded-index optical waveguides used in this cable system were made by a patented Corning doped deposited silica process. In this process, carefully

controlled materials that raise the refractive index of the core glass are introduced during deposition of the core.

Freedom from electromagnetic interference is a characteristic of optical waveguides that is particularly desirable in the Arnold Center installation, where accurate data transmission is essential. The characteristics are particularly important because real-time transmission reduces opportunities for error correction. Neither natural interference, such as lightning, nor manmade interference, such as that created by adjacent electromechanical equipment or cross-talk between fibers in the same cable, affects signals carried in optical waveguides. Also, waveguides do not radiate energy that might interfere with other equipment.

The practical application of waveguides on a demanding installation such as that at the Arnold Centre has only been possible recently. Six years ago the purest glass fibers of one-kilometer length could deliver only one per cent of the light introduced into them. However, steady improvement has been made, so that today as much as 80 per cent transmission has been achieved in the best optical waveguides of comparable length.

(205 S)

## Optical fibers are branching out

The purpose of telecommunication systems is to transmit information and data to specific destinations. For certain transmission applications, optical fibers are well on the way to competing effectively with conventional metal conductors. Viable methods of optical distribution of communications are also being established, and Siemens is now

presenting a branching unit for optical waveguides, developed with the support of the Federal Department of Research and Technology.

In an optical-fiber communication network, definite light components have to be branched off from the main optical waveguide. Since optical fibers do not readily lend themselves to branching, it was necessary to find a suitable optical distributor. Using a planar thick-film technology, research engineers at Siemens succeeded in realizing novel branching structures for optical fibers, based on the use of a light-sensitive plastic foil with a thickness of approximately 0.1 mm, corresponding to the diameter of the fibers. Any desired structure can be etched into this foil by photolithographic processes. The structure required for the waveguide branch is such that the two ends of the cut fiber meet with a slight offset. The light component escaping at the interface enters the foil and is guided along a curvature to a branching fiber. The amount of optical power coupled out depends on the offset of the ends of the main waveguide at the interface. The advantage of the described technology is that the lightguiding structure in the foil, and the guiding channels for the fibers, can be produced in a single operation. This fabrication method is very simple, while at the same time fulfilling the stringent requirements specified with respect to the accuracy of fiber alignment (tolerances of approximately  $\pm 3 \mu m$ ).

(204 S)

Alternating current flow can be detected and indicated using only four components. How?

See the inside of this month's mailing wrapper!

## introducing microprocessors (1)

A microprocessor is simply an extremely small processor, and a processor is part of a computer or other data processing system, so before delving into the intricacies of microprocessors it is first necessary to understand the operating principles of computers, and the function of a processor in a computer system.

A computer is basically a machine for processing data. The data to be processed is fed into the computer, and the results of the data processing are obtained at the output. The operations that are to be performed on the data are contained in a sequence of instructions known as the programme.

Apart from complexity, the major difference between a computer and say a simple pocket calculator lies in the programming. A calculator possesses a number of pre-programmed mathematical functions that can be called up at the push of a button, e.g. cos x, yX, log x, as well as the basic arithmetic functions +, -, x, ÷. A computer, however, possesses only basic arithmetic and manipulative logic functions 'if x > y, then . . .', and these must be written into the programme step by step. However, this makes a computer infinitely more versatile than a calculator. A calculator is limited in its operation to the mathematical functions available on its keyboard, whereas (within reason) any desired manipulation of data or complex mathematical operation may be performed by a computer by building the correct sequence of instructions into the programme.

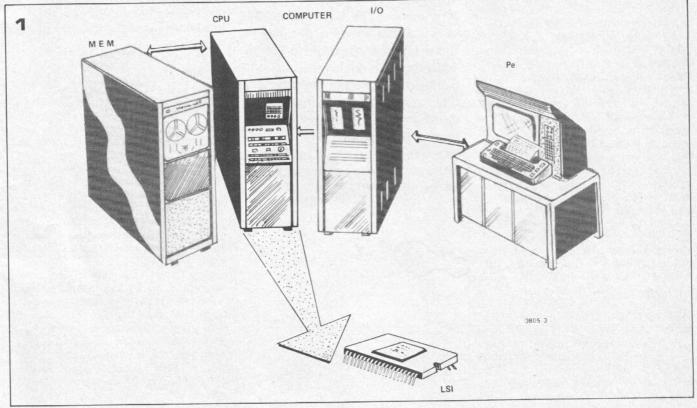

A typical computer system might consist of four units.

1. A separate (or sometimes peripheral) unit for preparation (and sometimes even verification) of programmes. This might consist of a teletype or visual display unit (VDU) and punched tape or card equipment.

2. A peripheral input/output unit such as tape/card reader to read in the programme and data, and tape/card punch to output the results.

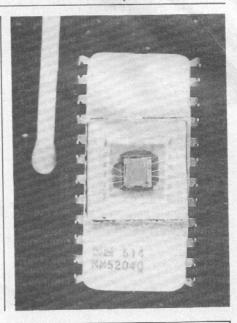

The programme preparation and input/ output units may frequently be combined, especially in applications where the computer and the user interact directly, e.g. by means of light pens, Over the past two decades increasing miniaturisation, and in particular the advent of integrated circuits, has revolutionised the electronics industry. Nowhere is this more true than in the field of digital electronics, especially in the area of data processing and calculating machines, where largescale integration (LSI) has made possible low price units of a small size and high performance unheard of even ten years ago. Currently, microprocessors are the 'in thing', so this series of articles is intended to provide a simple introduction to these extremely versatile devices.

voice recognition units etc.

3. A memory unit to store the data and programme instructions. The same memory may be used to store both data and programme, especially in small computers, or there may be separate programme and data memories.

4. A central processing unit (CPU). This carries out arithmetic operations, data comparison, manipulation and movement in accordance with the programme instructions.

Many readers will have seen photographs of early computers built using valves, and may have marvelled at their apparent complexity and wondered just why they were so complex. The answer is really very simple. After a few initial attempts to build computers operating in decimal notation it was quickly realised that to represent decimal numbers 0 to 9 electronically was not a very practical proposition when applied to a large computer system. It soon became apparent that it was much simpler to make computers operate in the binary number system, since this system uses only digits 1 and  $\emptyset$  (' $\emptyset$ ' is used instead of '0' for the digit, to clearly distinguish it from the letter 'O'), which can be represented electronically by 'on' and 'off' conditions.

A computer system must be able to handle and store large amounts of information (i.e. numbers), and to store one digit of a binary number requires an electronic circuit that can be set in one state or another depending on whether the digit is  $\emptyset$  or 1. Such a circuit is the common flip-flop. To store and handle many large numbers requires a correspondingly large number of flip-flops, and when one considers that in the days of valves each flip-flop would require one double-triode valve, it is not difficult to see why valve computers were so bulky.

In those days each of the four units of a computer might have occupied a room to itself, depending on the complexity of the computer system. The introduction of transistors made possible much smaller computers, and after the introduction of TTL and later MOS integrated circuits the size of computers could be reduced even further. Finally, with the perfection of LSI MOS tech-

Figure 1. A computer system comprises a memory unit (MEM), CPU, input/output unit (I/O) and peripherals. Development of LSI technology now means that the CPU can be integrated into a single IC — the microprocessor.

nology the microprocessor appeared on the scene. Thus the functions of the CPU, which in the days of valves occupied several racks of equipment, and in the days of TTL occupied several printed circuit boards, could now be integrated onto a single chip.

Of course large scale integration has also brought about a reduction in the physical size of memories, and large amounts of memory capacity can also be accommodated on one chip.

## **Applications of Microprocessors**

The most obvious use to which a microprocessor can be put, is to couple it to a memory and peripherals to build a microcomputer system. However, much more exciting applications are possible where the microprocessor is 'dedicated' to a particular task. A good example of this is the electronic sewing machine recently introduced by the Singer company. Until the advent of this machine patterned sewing was accomplished by purely mechanical arrangements of cams and levers operating in a fixed sequence. Once the production line was tooled up to produce a machine it was an extremely costly business to make any alterations to the patterns that could be produced. Using a microprocessor to control the sewing patterns all that needs to be changed is the programme.

A similar argument applies to automatic washing machines, which normally use cam timers to control the washing sequence. Here again the introduction of any new washing sequences would be extremely costly once the machine was past the prototype stage. Using micro-

processors the design can be made much more flexible. During the development phase the programme can be changed many times at relatively little cost and once it is perfected it can be 'frozen' into a memory for production use. Even if a design change is necessary during production it is simply a matter of substituting a memory with a new programme, which is considerably less costly than re-tooling to produce a new mechanical part.

In general, it is safe to say that microprocessors offer considerable advantages in applications where they can replace a large number of mechanical, electromechanical or electronic parts, such as in control applications in industry, in domestic appliances and in automobiles.

(to be continued)

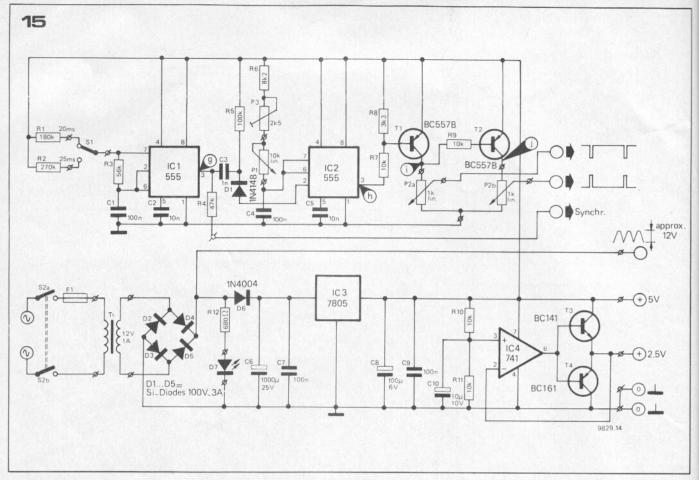

# FM-moins infercon—

A design for a simple mains intercom has already been published in the June '76 issue of Elektor. It was stated then that a future issue would contain a design for an improved version, which in a number of respects, would offer considerably better performance.

The original design was for an AM-system with roughly the same characteristics as most commercially available (AM-) devices. However, since there is very little that can be done to alleviate the problem of mains interference with such a system, it is often the case that users soon revert back to 'normal' intercom-installations.

The superior performance of the mains intercom described here is due almost entirely to its reduced sensitivity to interference. This is achieved by using an FM system. The advantages of using an FM- as opposed to an AM-transsystem were extensively mission 'modulation discussed in the article which appeared in the systems' February '75 issue of Elektor. Although the system does in fact employ a transmitter and a receiver, it is somewhat uncommon to use these terms when talking of an intercom system since it is the mains wiring which is being used as the medium to carry the

An intercom system is used in the first instance for the transmission of the spoken word, so that high fidelity reproduction is not required. This means that narrowband FM will give sufficient intelligibility for spoken signals. The use of a very narrow bandwidth has the advantage that, if the transmission and reception frequency is made adjustable over a reasonable range, then the number of available channels is thereby greatly increased. The system described here takes advantage of this possibility, since increasing the number of channels reduces the chance of one frequency overlapping with another and producing interference or 'splatter'.

The transmitting power of the intercom has to be fairly high to take account of the potentially very severe mains interference. However, under normal circumstances the output power (which may be varied) will be kept to a fairly low level in order to prevent the transmitter

The disadvantage of conventional AM-mains intercoms is that they are subject to the often highly disruptive effect of mains interference. The system described in this article however, obviates this problem by employing FM; in addition, by reducing the bandwidth to a minimum, the number of available channels is thereby greatly increased, so that there is little chance of interference ('splatter') between different intercom systems caused by channel overlap.

being picked up outside the building. The construction of the intercom is simplified by the fact that a complete station, consisting of a transmitter, a receiver and a supply section, can be mounted on one printed circuit board. In addition the circuit is simplicity itself as far as tuning is concerned.

## Design

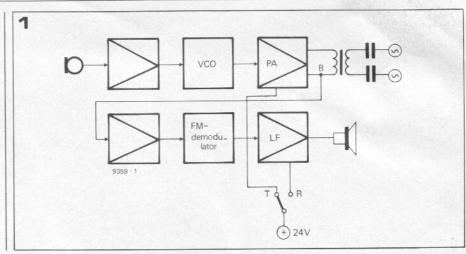

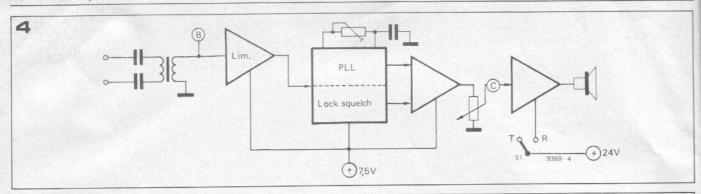

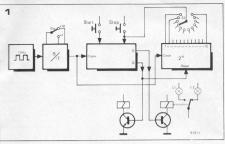

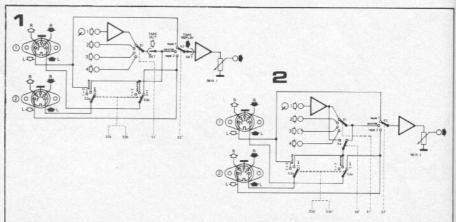

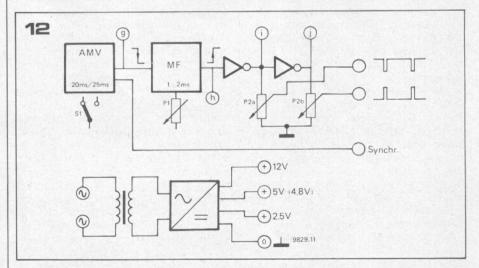

Figure 1 shows the block diagram for a complete intercom station. The transmitter and receiver sections interconnect at point B, so that the mains connection functions as both the in- and output of the station.

The transmitter section is shown on the upper half of the diagram. The signal from the microphone is first amplified, limited and filtered, then used to frequency modulate an oscillator. After being amplified, the resulting FM-signal is fed into the mains via an isolation transformer.

Signals transmitted from other stations are picked up by the transformer and fed to the receiver section. After being amplified and limited, the received signal is demodulated and fed, via a simple audio-amplifier, to a loudspeaker. Switching between 'speak' and 'listen', i.e. between transmit and receive, is accomplished by switching the supply voltage between the output stage of the transmitter and the AF-amplifier of the receiver.

## The Transmitter

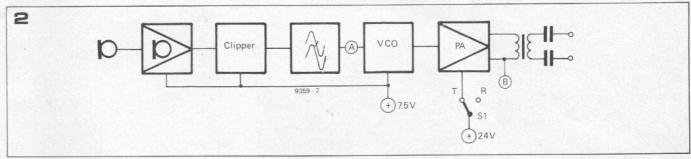

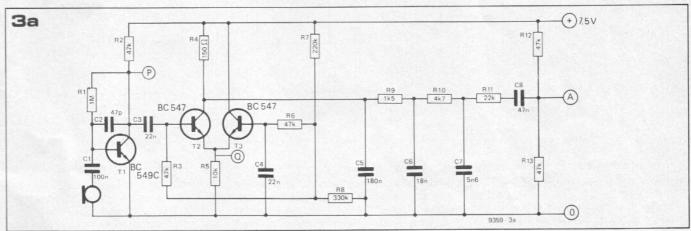

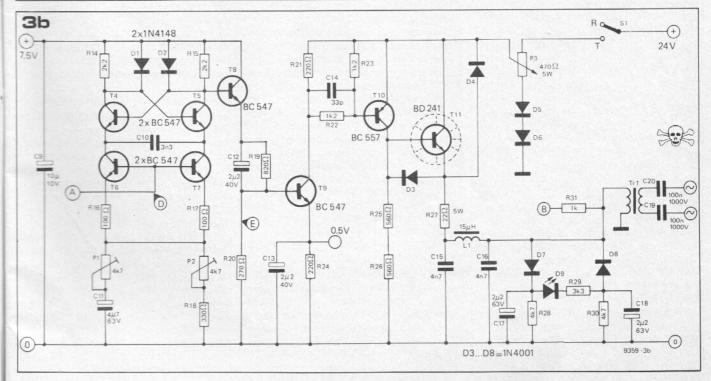

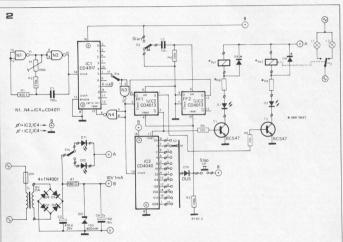

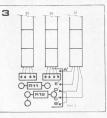

Figure 2 shows a more detailed block diagram of the transmitter section of the intercom. The circuit diagram for the first three blocks is reproduced in figure 3a, whilst figure 3b shows the circuit diagram for the rest of the transmitter.

As is apparent from the block diagram, the signal from the microphone is first amplified by the stage round T1. In order to reduce the bandwidth of the transmitted signal to a minimum approx. 10 kHz in this case), T1 is followed by a clipper, consisting of the differential stage round T2/T3. Although the signal is severely clipped, the intelligibility of the audio signal is virtually unaffected. The clipper is

Figure 1. Block diagram of a complete station of the mains intercom. The station, together with the supply section, can be mounted on a single circuit board.

Figure 2. Block diagram of the transmitter. After being clipped and filtered, the microphone signal is used to modulate the frequency of a VCO. The resulting FM-signal is then amplified and fed to the mains via an isolation transformer.

Figure 3a. The circuit diagram of the microphone preamplifier, clipper and lowpass filter.

Figure 3b. The circuit diagram of the VCO and the output stage of the transmitter.

followed by a lowpass filter (R9, R10, R11, C5, C6 and C7) with a cutoff frequency of approx. 5 kHz, which ensures that the sidebands of neighbouring channels do not overlap causing splatter.

The resulting signal (we have now reached figure 3b) is used to modulate the frequency of the VCO built up round T4, T5, T6 and T7. The size of the frequency deviation can be adjusted by means of P2. The frequency of the VCO (i.e. the desired channel) is tuned using P2; the range of the oscillator runs from approx. 70 kHz to approx. 500 kHz.

frequency-modulated oscillator The signal is then fed via the buffer stage T8 to a power amplifier consisting of T9, T10 and T11. The latter two transistors are connected as class-C amplifiers. However the efficiency of the output stage is not as great as one might expect, since the stage has no facility for tuning, thereby making it impossible to match to the load. Although an adjustable matching network would considerably increase the power of the transmitter, it was decided that it would not be practicable in this case. The reason for this is that when using more than one channel, it is not sufficient merely to

alter the VCO-frequency to select a different channel, the matching of the output stage would also need to be adjusted accordingly, thereby making the system much more complicated to operate.

Operating the output stage in the wideband mode guarantees an output power of at least 1 W over the entire frequency range of the VCO. The transmitter power is adjusted by means of P3 (a 5 W type should be used).

Components D3, D4, D7, D8, C17 and C18 protect the output stage of the transmitter from possible voltage transients occurring on the mains. LED D9 is included to provide a visual indication of the transmitter power. Power transistor T11 should be fitted with a heat sink (for which sufficient room has been left on the printed circuit board).

## The Receiver

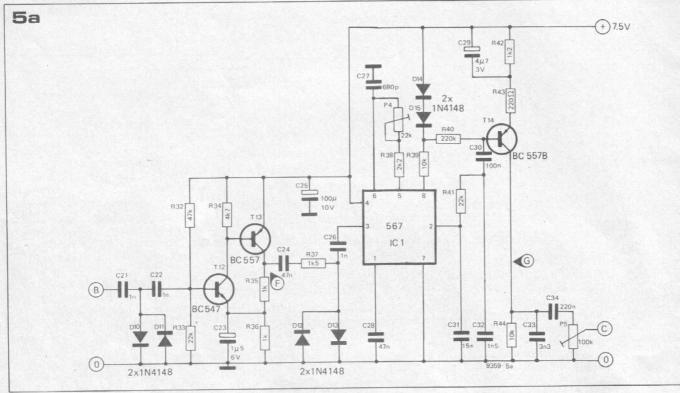

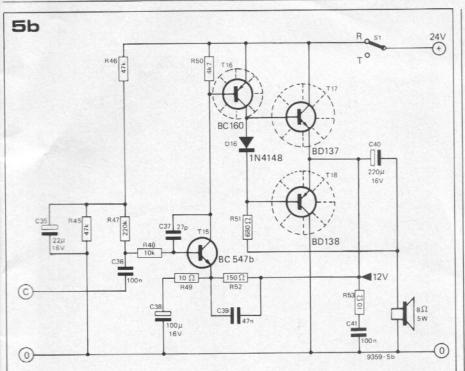

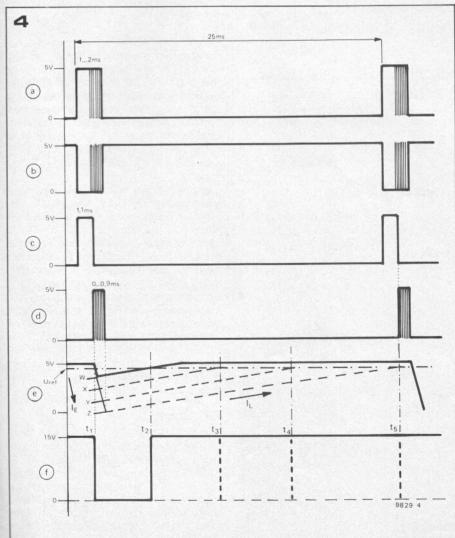

Figure 4 shows the block diagram of the receiver section of the intercom. The circuit diagram of the most important part of the receiver, namely the phase locked loop, is given in figure 5a, whilst figure 5b shows the circuit diagram of the last block in figure 4, i.e. the AF-amplifier.

Incoming signals from other intercom stations are fed via the isolation transformer Tr1 (see figure 3b) to the input of the receiver. The output of the transmitter and the receiver input are thus connected directly to one another (point B). However, in order to prevent the clamping diodes at the input of the receiver from burning out when the station is transmitting, a series resistor (R31 in figure 3b), is included.

For the same reason that there is no facility for matching the transmitter output stage, the receiver input is also untuned. For the present application the receiver is sufficiently selective as it is, and a wideband input has the added advantage that it is less susceptible to shock excitation caused by transient voltage peaks.

The block marked 'Lim.' in figure 4 represents the stage which amplifies (to approx. 1 Vpp) and limits the input signal. This is done by T12/T13 and D12/D13 respectively. The signal is then demodulated using a phase locked loop fitted with 'lock squelch', i.e. the receiver will only deliver an output when the PLL is locked in.

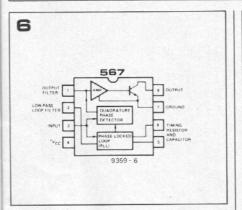

As is apparent from figure 5a, this stage employs an IC (IC1). The IC used (available from, among other, Signetics

Figure 4. Block diagram of the receiver. After it has been amplified and limited, the received signal is demodulated in a PLL with 'lock squelch'. The demodulated signal is fed to the loudspeaker via a low-frequency amplifier.

Figure 5a. The circuit diagram of the high-frequency section of the receiver. IC1 contains a PLL FM-demodulator. The output transistor of the IC, together with T14, forms the lock squelch.

Figure 5b. The low-frequency amplifier of the receiver.

Figure 6. Internal block diagram of the tone decoder IC, type number 567.

Figure 7. The supply, which, along with the receiver and transmitter is mounted on the circuit board.

B30 C2 200

R55

BC 140

+ 7.5 V

R54

R55

BC 140

T19

R54

R54

R54

R55

R54

R54

R55

R55

R54

R55

R54

R55

R55

R54

R55

and Exar under type number 567) is a tone decoder, and contains a PLL, a phase detector, a comparator/amplifier and a driver amplifier with open collector. When the received signal is within the capture range of the PLL, the PLL locks on to the input signal. The built-in detector functions as a 'lockindicator'; when the PLL is locked in, there is a sharp increase in DC-output voltage of the detector. This voltage is converted by the amplifier and output driver transistor into a logic state. In the quiescent state pin 8 of the IC is high, whilst during lock, the logic state at this pin is low.

ıt

T

ıt.

e

0

er

0

it

d

0

4

ıt

d

n

p

1e

it

ge

The FM-input signal is demodulated by taking as the LF-signal the control voltage for the PLL-VCO present at pin 2. The lowpass filter which is connected to this pin is formed by C31 (see figure 5a) together with a resistor in the IC. The LF-signal is fed via R41 and C30 to the base of transistor T14. However the DC-bias voltage of this transistor is determined by the logic state at pin 8 of the IC. The transistor will turn on only when the PLL is in lock and pin 8 is low. If the input frequency band is outside the capture range of the PLL, the latter will not lock in, and the low frequency signal at the output will be suppressed, hence the term 'lock squelch'.

By means of P4 the free running frequency of the PLL-VCO can be tuned to the centre frequency of the transmission. The range of the PLL-VCO is roughly the same as that of the VCO of the transmitter.

The LF-signal is fed to the power amplifier via preset potentiometer P5, which functions as a volume control. P5 may be replaced by a normal pot. if a manual volume control is required. As figure 5b makes clear, the power amplifier is of a very simple design, given the fact that there is no need for hi-fi reproduction. In the absence of a signal no quiescent current flows through the output stage; with a supply voltage of 24 V the circuit will deliver 5 watts to an 8 ohm loudspeaker.

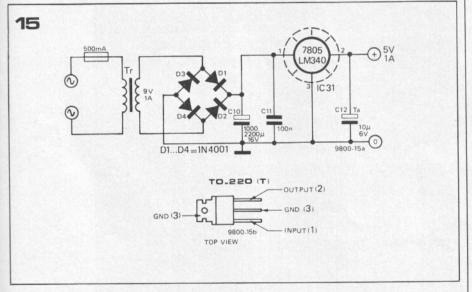

## The Supply

It will have become clear from the foregoing that two separate supply voltages are needed for the intercom. Most of the circuit operates at 7.5 V, but for the output stage of the transmitter and the LF-amplifier in the receiver, a 24 V supply is necessary. The 24 V supply is switched between the transmitter-output stage and the LF-

amplifier by means of transmit/receive switch S1.

For ease of construction, the supply for the entire intercom is also mounted on the printed circuit board. Figure 7 shows the circuit diagram for the supply section, which although fairly simple, is perfectly satisfactory for this application. The 24 V supply is taken direct from a rectifier circuit, whilst the 7.5 V supply is obtained using a simple regulator, consisting of a transistor and a zener diode. Supply transformer Tr2, which of course cannot be mounted on the p.c.b., should have a secondary voltage of 18 V and supply a current of 1.5 A.

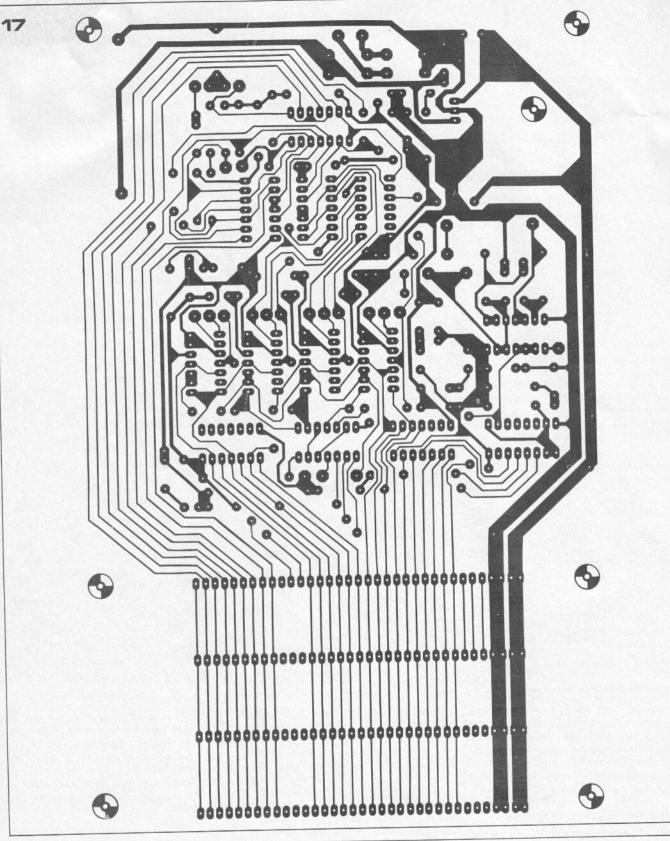

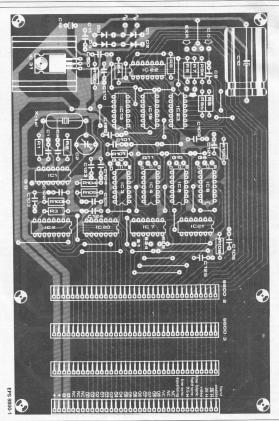

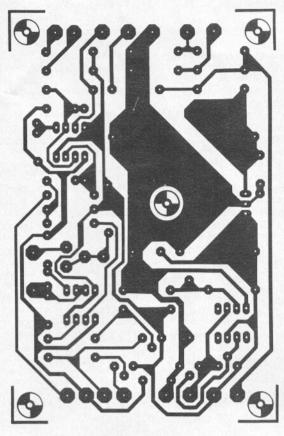

## Construction

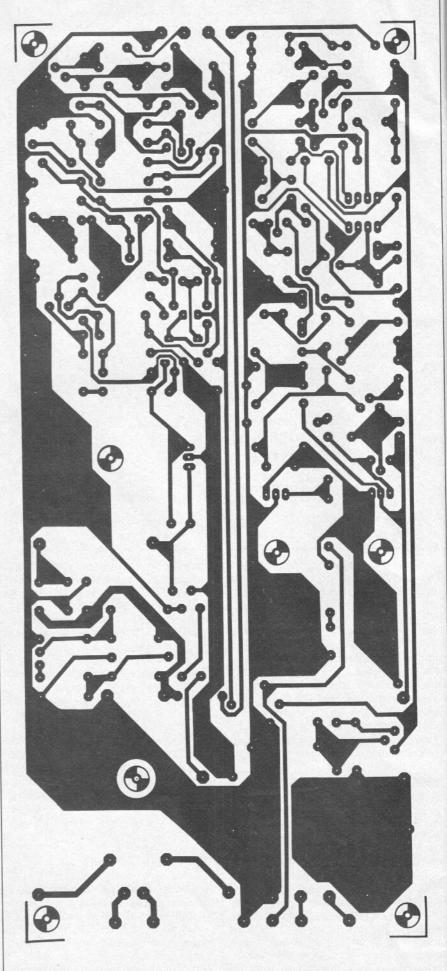

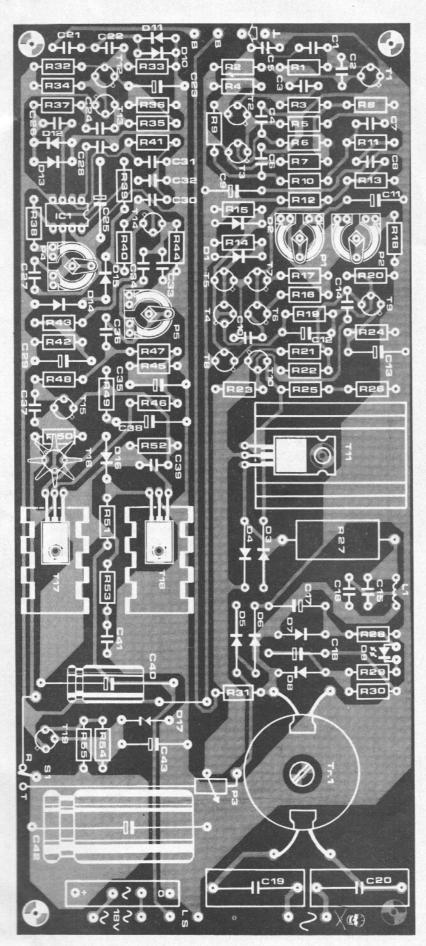

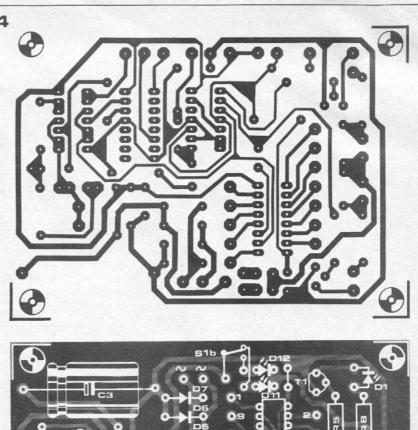

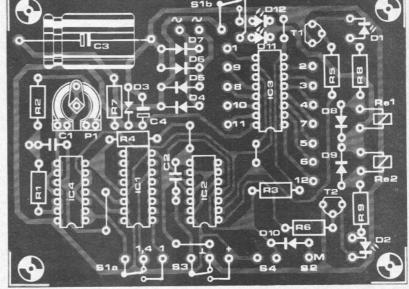

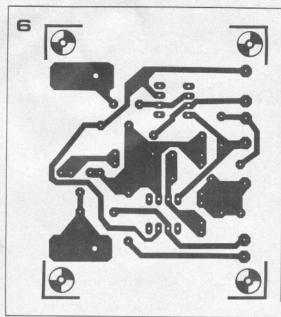

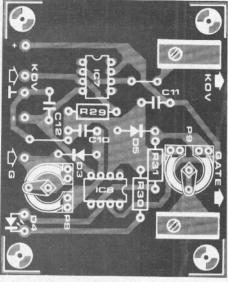

Figure 8 shows the component layout and copper side of the printed circuit board. The construction of the intercom should present few difficulties, providing the listed component values are adhered to. The only problem may be the isolation transformer Tr1, which has to be selfwound. A pot core without an air gap, 30 mm in diameter and 19 mm high, should be used. The primary winding consists of 48 turns of enamelled copper wire 0.3 mm thick; 24 windings of the same wire will suffice for the secondary

Parts list for figure 8: a complete station (figures 3a, 3b, 5a, 5b and 7)

R29,R54 = 3k3

R49,R53 =  $10 \Omega$

$P3 = 470 \Omega/5 W$ P4 = 22 k preset

P5 = 100 k preset

R51 = 680  $\Omega$

R31,R35,R36 = 1 k

P1,P2 = 4k7 preset

R1 = 1 M

R2, R3, R6, R12, R13, R32,

R45,R46 = 47 k

$R4,R52,R55 = 150 \Omega$

R5,R39,R44,R48 = 10 k

R7,R40,R47 = 220 k

R8 = 330 k

R9,R37 = 1k5R10,R28,R30,R34,

R50 = 4k7

R11,R33,R41 = 22 k

R14,R15,R38 = 2k2

R16,R17 = 100  $\Omega$

$R18 = 330 \Omega$

$R19 = 820 \Omega$

$R20 = 270 \Omega$

$R21,R24,R43 = 220 \Omega$

R22,R23, R42 = 1k2

R25,R26 = 560  $\Omega$

$R27 = 22 \Omega/5 W$

## Capacitors:

C1,C30,C36,C41 = 100 n

C2 = 47 p

C3,C4 = 22 n

C5 = 180 n

C6 = 18 n

C7 = 5n6

C8,C24,C28,C39 = 47 n

$C9 = 10 \mu/10 V$

C10,C33 = 3n3

$C11 = 4\mu7/63 \text{ V}$

$C12,C13 = 2\mu 2/40 \text{ V}$

C14 = 33 p

C15,C16 = 4n7

$C17,C18 = 2\mu 2/63 \text{ V}$

C19,C20 = 100 n/1000 V

C21,C22,C26 = 1 n

$C23 = 1\mu 5/6 \text{ V}$

$C25,C43 = 100 \mu/10 V$

C27 = 680 p

$C29 = 4\mu7/3 \text{ V}$

C31 = 15 n

C32 = 1n5

C34 = 220 n

$C35 = 22 \mu/16 V$

C37 = 27 p

$C38 = 100 \mu/16 V$

$C40 = 220 \,\mu/16 \,V$

$C42 = 4700 \,\mu/35 \,V$

## Semiconductors:

T1 = BC549 C

T2 . . . T9,T12 = BC547

T10,T13 = BC557

T11 = BD241

T14 = BC557 B

T15 = BC547 B T16 = BC160

T17 = BD137

T18 = BD138

T19 = BC140

D1,D2,D10 . . . D16 =

1N4148

D3 . . . D8 = 1N4001

D9 = LED

D17 = BZX79-C 8V2

(or equ. 8V2 zener)

IC1 = 567

## Miscellaneous:

L1 = choke 15µH

Tr1 = pot core tranformer

(see text)

Tr2 = supply transformer 18 V/1.5 A

B = bridge rectifier B30C2200

S1 = SPDT switch

8

winding. The above pot cores are available from Mullard under type number FX 2241, and from Siemens. type number B65701-L0000-R026 (or equivalent).

The power transistor in the transmitter and the two power transistors in the LF-amplifier (T17 and T18) should be fitted with a heat sink.

## Tuning

When two intercom stations have been completed and are functioning satisfactorily (which can be checked by measuring the voltages at the points indicated in the circuit diagram), the tuning procedure - which is not difficult - can begin:

\*switch both stations on and set one to 'transmit' and the other to 'receive'.

\*set P3 for maximum transmitting power; LED D9 on the transmitter should now light up.

\*set P2 (transmission frequency) to mid-position.

\*adjust P4 on the receiver until the PLL audibly locks in on the transmitted signal; continue to adjust P4 until the PLL goes out of lock; P4 should then be set to the position midway between these two points.

\*connect a microphone to the transmitter and set P1 for maximum fre-

quency deviation.

\*hold the microphone of the transmitter close to the loudspeaker of the receiver thus producing 'howl round'. By means of P5, set the receiver to a reasonable volume.

\*still holding the microphone close to the loudspeaker, use P1 to adjust the frequency deviation of the transmitter until the acoustic feedback produces a much smoother sound, with no audible evidence of overloading. The resulting position for P1 should give a reasonable volume with minimal distortion when receiving spoken signals.

\*Finally, set the transmit/receive switch of both stations in the alternative position, and repeat the above procedure for the other transmitter and receiver. A different transmission frequency should be chosen in order to

avoid possible interference.

Once the tuning procedure has been completed, it is advisable, in the event of severe interference or of heavy signal losses due to transmitting between different phases, to experiment with the system in order to find the optimum transmission frequency. This also avoids the potential problem of a number of users setting P2 in the identical midposition, thereby increasing likelihood of channel congestion.

In some cases, where severe mains interference is present, it may prove helpful to add a small resistor (say  $56 \Omega$ ) in parallel with the primary of Tr1 - i.e. between the R31/D8 junction and supply common.

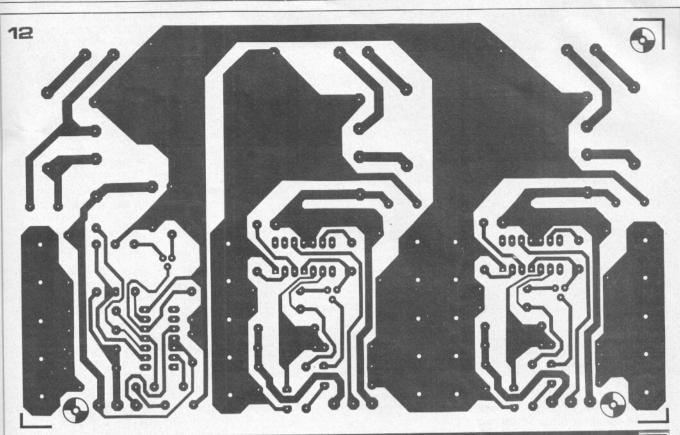

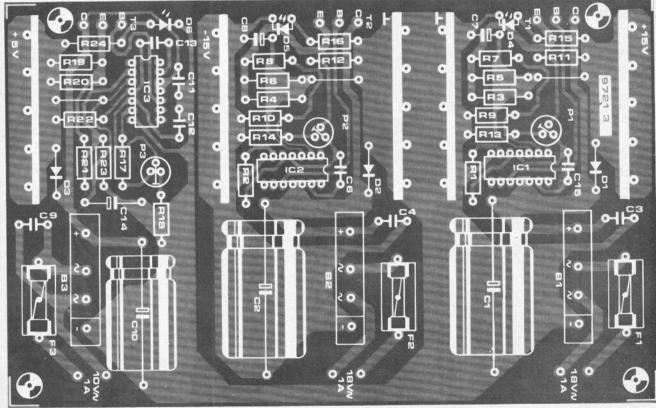

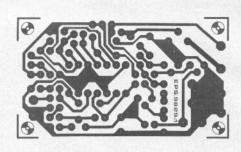

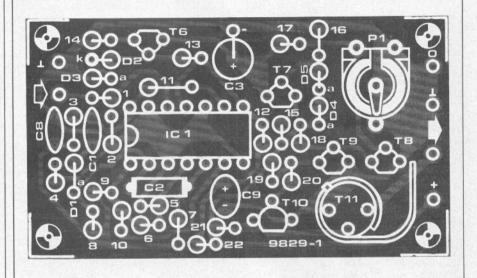

Figure 8. Copper side and component layout of the circuit board for the mains intercom.

## In Conclusion

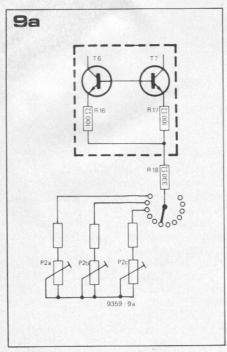

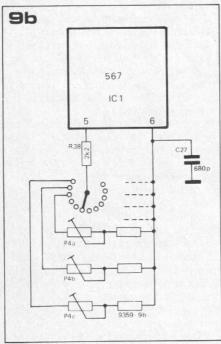

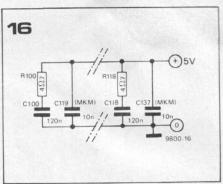

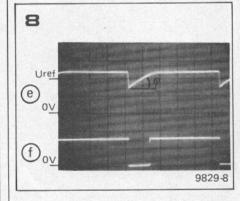

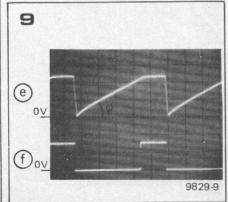

If, as is shown in figure 9a, a multi-way switch, along with a number of fixed resistors connected in series with preset potentiometers, is used to replace P2, then the result is a true multichannel transmitter. A similar alteration to the frequency-determining section of the receiver (figure 9b) thus converts the system into a complete mains-transceiver.

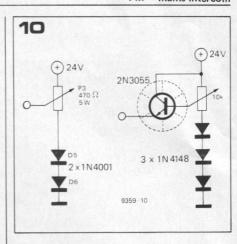

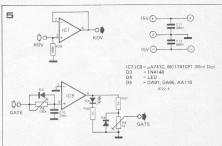

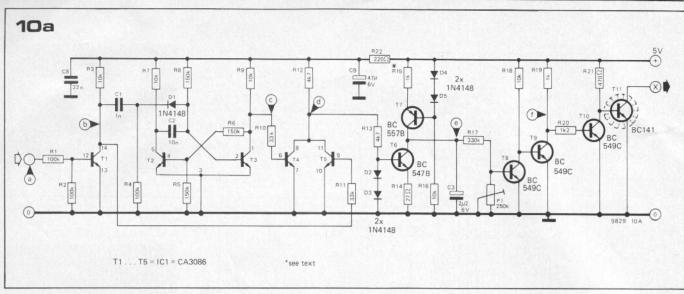

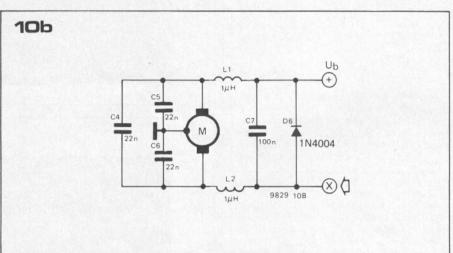

Should difficulties occur with the 5 W wirewound potentiometer (P3 in figure 3b) used to regulate the transmitting power, an alternative arrangement is shown in figure 10. The replacement circuit, shown on the right of the diagram, employs a more conventional type of potentiometer and a power transistor, which should of course be fitted with a heat sink.

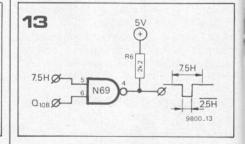

## Babyphone extension

A large number of mains intercoms are used as babyphones or baby-alarms. It is important that, before an intercom is used for this purpose, it be fitted with a voice-operated control. If this is omitted, the result is that a continuous, more or less unmodulated carrier signal is being transmitted, which, in the case of widespread use, will soon lead to channel congestion. In addition, those present in the same room as the receiver station will be subject to a variety of background noises produced by the intercom.

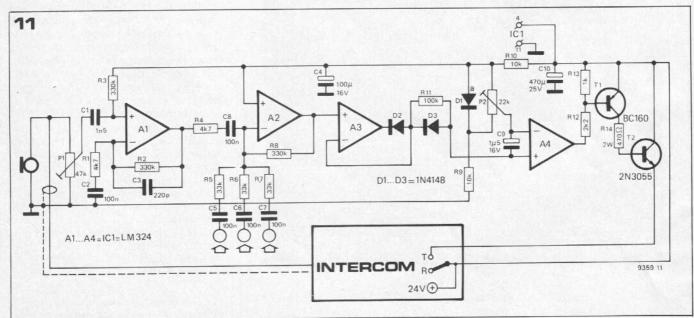

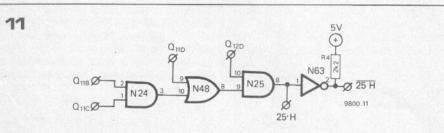

For this reason the following add-on circuit (see figure 11) offers a babyphone extension for the mains intercom, which will ensure that the intercom is only switched on when the alarm has been actuated.

The signal from the microphone is first amplified by A1 and A2. The latter amplifier stage can also be used to amplify the signals from up to three separate alarm-signal sources of the type described in Elektor 19, November 1976, p. 1121 and 1141. A3, together with D2 and D3, functions as a

Figure 9. Extension to switchable multichannel transceiver.

Figure 9a shows the necessary alterations to the frequency-determining section of the transmitter VCO; figure 9b shows the alterations to the VCO frequency in the PLL of the receiver.

Figure 10. On the left is the original circuit, whilst an alternative method of regulating the power of the transmitter is shown on the right (cf. figure 3b).

Figure 11. Circuit diagram of babyphone extension for mains intercom.

rectifier, and feeds a DC voltage to A4, which operates as a trigger, the threshold voltage of which may be adjusted by means of P2. With a sufficiently large input signal, the output of A4 is pulled low, causing T1 and T2 to turn on and switch the supply voltage to the intercom. The value of R14 is such that the maximum current through T2 is 1A, which should prove sufficient in the majority of cases.

The adjustment procedure is as follows: the slider of P2 is turned fully towards the anode of D1 and P1 is used to adjust the circuit to the desired sensitivity. If the circuit fails to trigger with P1 set for maximum sensitivity, then the trigger threshold can be lowered by means of P2.

In addition to its use with a mains intercom, the circuit can be adapted for radio ham applications, since:

\*the circuit functions with supply voltages equal to or greater than 6 V

\*the circuit offers the possibility of VOX (Voice operated transmission)

\*A1 and A2 can be used as microphone amp and clipper.

## Multipurpose time switch

Summer Circuits 1977 (E27/28), circuit no. 6. The operation of this circuit is such that only half of the mains period is multiplied to obtain the required timing period. The maximum timing interval is therefore 0.01 x 2<sup>24</sup> seconds, or approximately 46.6 hours. In the example given for a 24-hour timer, an extra nought should be added at the end of the binary number. It will be noted that the A1...A8, B1...B4 and C1...C4 connections shown in the circuit diagram are correct for this application.

The last paragraph is perhaps misleading. The CMOS NAND gates mentioned are actually N8 and N4 in the circuit.

## Automatic NiCad charger

Summer Circuits 1977 (E27/28), circuit no. 13. In the diagram, two resistors are shown as R6. The one in the top left hand corner should be R4 = 330  $\Omega$ . Furthermore, it should be noted that

Furthermore, it should be noted that although S1 is shown on the p.c.board,

only one pushbutton is required for any number of boards as shown in the circuit diagram.

## 0 . . . 10 V supply

Summer Circuits 1977 (E27/28), circuit no. 24. A resistor  $R_X$  is shown on the component layout for the printed circuit board. If a wire link is used here, the circuit shown in figure 1 is obtained. Alternatively, a fixed resistor at this point can be used to reduce the maximum output voltage obtainable to any desired value.

## Spot-frequency sinewave generator

Summer Circuits 1977 (E27/28), circuit no. 25. The input pinning of IC2 and IC3 are shown incorrectly. In both cases, the inverting input should be pin 2 and the non-inverting input should be pin 3.

## Stereo pan pot

Summer Circuits 1977 (E27/28), circuit no. 35. The value of P1/P1' is not shown in the diagram. This should be a twin 10 k lin potentiometer.

## Reaction speed tester

Summer Circuits 1977 (E27/28), circuit no. 54. Very little remains of the identification of the preset potentiometer between pins 6 and 7 of IC1... This is P1, and the value is 100 k. If desired, C1 can be reduced to 390 n and P1 can be readjusted until clock pulses are produced every 10 ms.

## Short-wave converter

Summer Circuits 1977 (E27/28), circuit no. 64. In the text, for BFO read VFO (variable frequency oscillator).

### Phase

Summer Circuits 1977 (E27/28), circuit no. 70. T1 ... T6 are given in the circuit as BC245Cs. This should have read BF245C.

## Voltage controlled monostable

Summer Circuits 1977 (E27/28), circuit no. 82. The positive end of the electrolytic should be connected to pin 11 of the IC, the negative end to pin 10.

## Drill speed control

Summer Circuits 1977 (E27/28), circuit no. 104. A better position for L1 is in series with the connection between the top of C1 and the top of R1 - C1 is then connected direct across the mains. R1 should be a 1 Watt type.

## 3½ digit DVM

Summer Circuits 1977 (E27/28), circuit no. 105. T6 is shown as an E300. Although this FET will work in the circuit shown, its pinning does not correspond with the p.c.board layout. The correct type for use on the p.c.board is a BF245.

# working perspex

Acrylic sheet is relatively inexpensive, and is available both clear and opaque in a variety of colours. 3 mm thick sheet will normally be adequate for all but the largest cabinets. Acrylic sheet is normally obtained covered by a protective paper film. This simplifies marking out, and to avoid scratches the paper should be retained until after drilling and sawing operations are complete.

## Drilling

A certain amount of care must be taken when drilling perspex to avoid splintering and cracking around the hole. Drills should always be kept as sharp as possible. When drilling small holes a normal twist drill may be used and the drill speed should be kept high. However, prolonged high-speed drilling should be avoided as friction may cause the perspex to melt. It is much better to drill a hole in several 'bites', allowing the drill and workpiece to cool down in

Almost every electronics enthusiast likes to house his lovingly constructed projects in an attractive case or cabinet. Although a wide range of cabinets is now available from various manufacturers it is still often difficult to find a case which meets the exact requirements of a particular project, or is within the budget of the constructor. Attractive cabinets can be fabricated from acrylic sheet such as Perspex TM or Plexiglas TM with much simpler tools than those required for metalworking.

between, and clearing swarf from the drill flutes.

Larger holes are best cut with a screw auger, since this cuts the hole from the outside inwards and splintering is less likely.

Very large circular holes may be cut using a hole saw or tank cutter. When cutting large holes, care should always be taken to clamp the work securely in case the drill or cutter should grab, which might otherwise lead to the loss of several fingers.

## Sawing

Straight cuts can be made using a normal hacksaw or a power saw with a fine tooth blade. Large cut outs of any shape may be made using a jigsaw or padsaw, after first drilling a hole into which the saw blade can be inserted. As with drilling, care must be taken to avoid melting the acrylic sheet, and frequent stops should be made to clear swarf from the saw blade, since it has a marked tendency to clog the teeth.

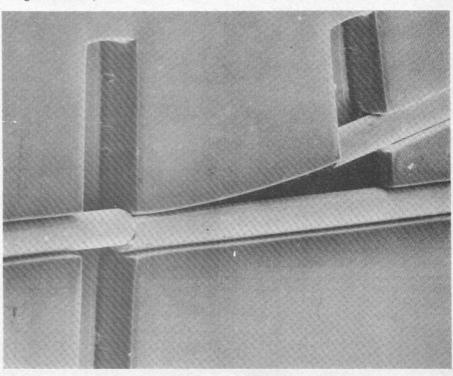

## Bending

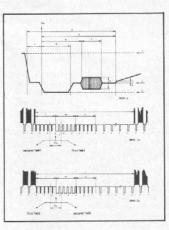

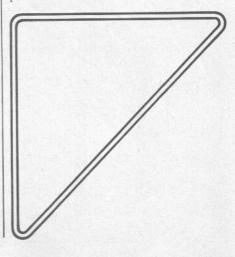

A useful quality of acrylic sheet is that it can easily be bent after softening by heat. Only the portion of the sheet where the bend is to occur is heated, and figure 1 shows a simple bending jig that can be mounted at the edge of a workbench. Current is passed through a length of resistance wire mounted along the edge of the bench just below the acrylic sheet. The wire, and hence the sheet, heats up, and the sheet can easily be bent upwards. If a sharp bend is required then a wooden batten may be clamped over the sheet along the bending line. However, sharp bends will cause some 'waisting' of the sheet at the bend.

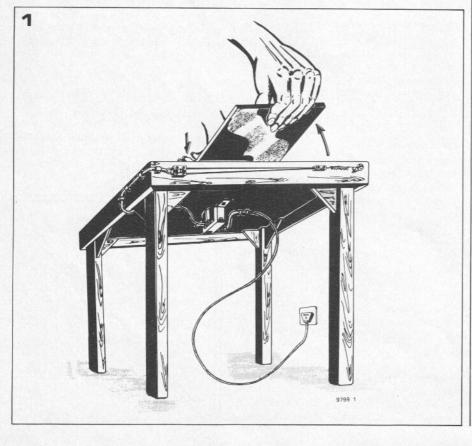

The mechanical details of the bender are extremely simple. The current supply is brought to a 'chocolate block' connector which is fixed to the bench. The resistance wire is a loop which goes out from the connector to a second connector and back again. The second connector is fixed to a coil spring that keeps the wire under tension so that it will not go slack as it heats up and expands.

The power rating of the transformer

should be around 80 watts, and for safety reasons the secondary voltage should not exceed about 24 V. The resistance of the wire can easily be calculated from the equation:

$$R = \frac{V^2}{P} \text{ where } R = \text{resistance}$$

$$V = \text{transformer power}$$

$$P = \text{transformer power}$$

P = transformer power

The length of wire required can then be found by dividing the required resistance by the specific resistance (ohms per metre) of the wire. For example, if the transformer secondary is 24 V at

the transformer secondary is 24 V at 80 W then

$$R = \frac{24^2}{80} = 2.81 \Omega$$

. If the

specific resistance of the wire is  $2.5 \Omega/m$  then the length required is  $\frac{2.81}{2.5}$  or 1.12 m.

Alternatively, if a particular length of wire is required, for example to fit a certain bench, then the required specific resistance can be obtained by dividing the resistance by the length required. Obviously the wire gauge chosen should not be so thin that it will quickly burn out in use, but there is obviously much scope for individual ingenuity in constructing a bending jig.

The basic circuit of the bender is shown in figure 1a. The heating effect may be controlled by driving the transformer from a 100 VA Variac as shown in figure 1b, or by driving the heater direct from an isolating Variac as shown in figure 1c. On no account should the heater be driven direct from a normal Variac, however, as this is not isolated from the mains.

To use the bender the bend line is placed directly over the heater and the heater is switched on for about thirty seconds, after which the acrylic sheet should bend easily. Care should be taken not to bend at too low a temperature as this can cause stress lines and cracks. When making a right angle bend it is best to bend the sheet just past ninety degress as it will tend to 'unfold' as the material cools. With a little practice bends with very clean, straight edges can easily be achieved.

Bending is best carried out after all drilling operations have been completed, as otherwise the sheet cannot easily be supported while drilling. The only exception to this rule is if a large hole is to be cut very close to a bend. This should be cut after bending, as otherwise the bending operation may distort the hole.

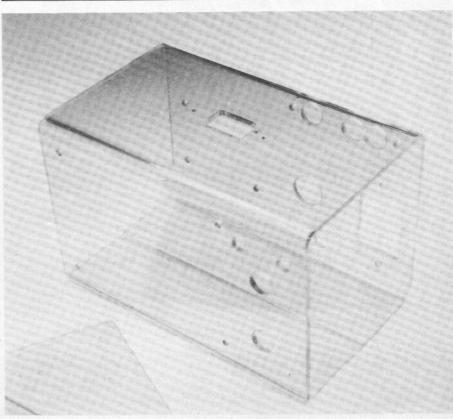

Cabinets may be constructed from a single sheet in 'wrap-around' form with two endplates, as shown in the accompanying photograph. In this case only one seam is required on the main part of the box, and from an appearance point of view it is best to place this at the base of the cabinet. The end cheeks can be made of acrylic sheet or, for a contrasting appearance, wood. Wood also has the advantage that it can easily be grooved to accept the edges of the box. A transparent acrylic box with

wooden end cheeks can make an attractive housing for an instrument such as a digital clock, allowing all the 'works' to

Another useful method of construction is to make three sides of the cabinet in a 'U' shape from a single acrylic sheet. The other three sides are also made in the form of a 'U' which mates with the first 'U'. The advantage of this method is that one part of the cabinet can form the front panel, base and back panel with components mounted on it, while the other part is simply a lift off lid.

Seams and joints may be made using acrylic adhesive which is available from suppliers of acrylic sheet.

## Lettering

Acrylic cabinets, like any other cabinet, can be attractively labelled using instant dry transfer lettering. After rubbing down the letters firmly they can be sprayed with protective lacquer to prevent damage. The lacquer should be of a type that dries to a hard gloss finish, as the matt types of lacquer supplied for use with instant lettering tend to attract dirt very quickly.

TM-Perspex and Plexiglas are registered trade marks.

Figure 1. Construction of a simple bending jig for acrylic sheet work.

Figure 2. Three possible methods of powering the heater for the bending jig.

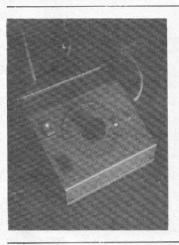

Photo. An almost complete acrylic sheet cabinet, showing the main assembly and the two end cheeks.

## logiarithnnic dorkroom tin

## Linear or Logarithmic

When taking a photograph, the exposure of the film can be varied in two ways, by altering the shutter speed and by altering the aperture setting of the camera. Opening the aperture by one stop doubles the amount of light falling on the film, i.e. the aperture setting is calibrated logarithmically.

In the darkroom, when printing or enlarging, the exposure of the photographic paper is varied by altering the time for which the lamp is switched on. Here again, a logarithmic scale is appropriate. For example, consider a timer with a linear scale calibrated from 0 to 100 seconds in intervals of five seconds. The first 'stop', from 5 to 10 seconds, will double the exposure time. However, at the top end of the scale a change of exposure time from 95 to 100 seconds would have little effect on the final print, as this last stop represents only a 5% change in exposure time. This means that: a) the timing scale is too finely calibrated at the upper end, but is probably too coarsely calibrated at the lower end, and b) the range of such a timer is limited, since to extend it to say 200 seconds would require a 40-way

This objection could admittedly be overcome by building a digital timer programmed by thumbwheel decade switches, but there would still remain the basic difficulty of having to estimate how much to increase or decrease the exposure time in order to obtain a lighter or darker print.

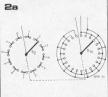

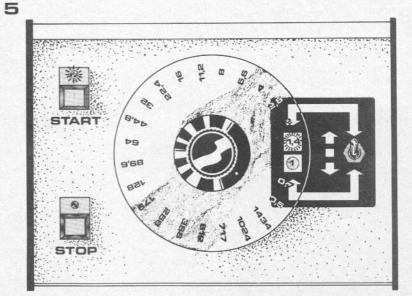

In the circuit given here, each increment of the timing switch doubles the exposure time, so each switch position will have the same effect on the density of the final print. If a finer increment is required a 'half-stop' position is provided that increases the exposure time by a factor of  $\sqrt{2}$ .

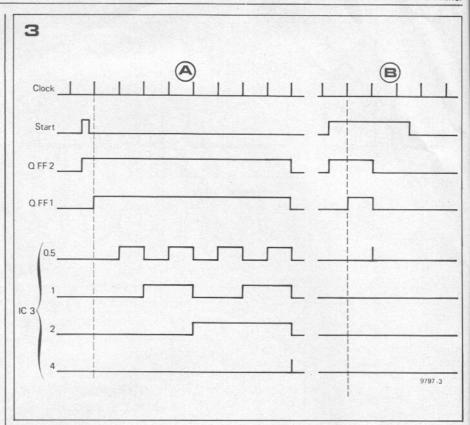

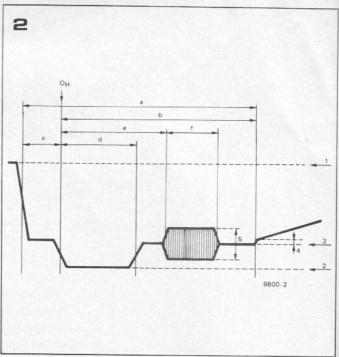

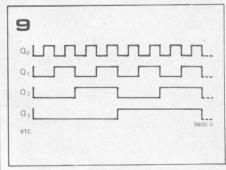

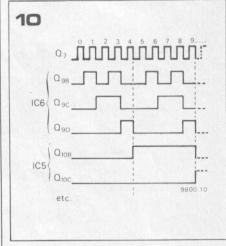

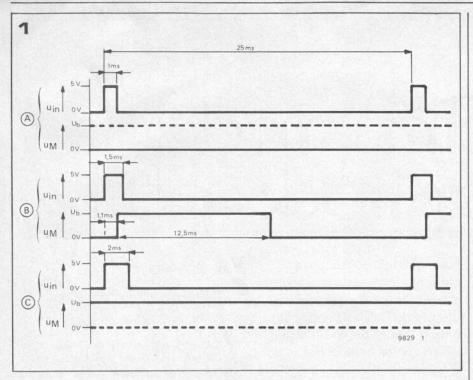

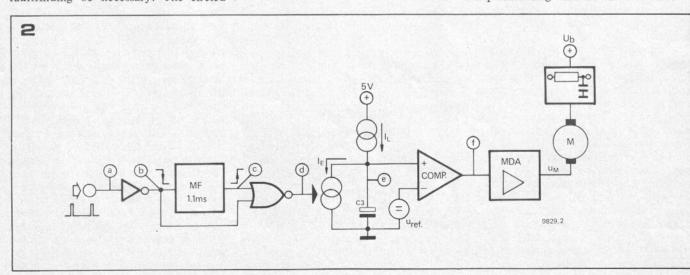

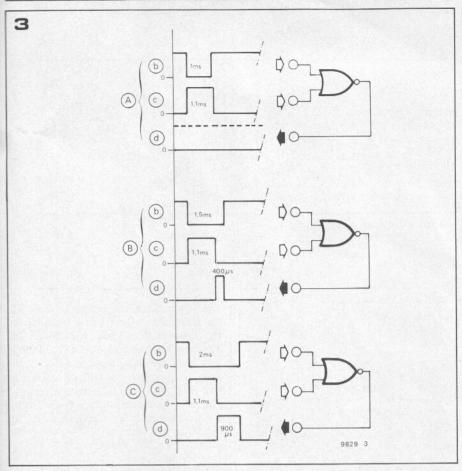

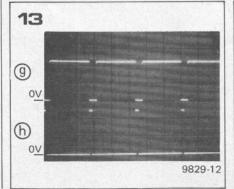

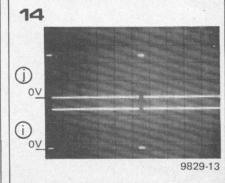

A block diagram of the timer is given in figure 1. Pulses from a 10 Hz clock generator are divided by a counter whose division ratio can be set to either 5 or 7 by means of S1a. This means that with S1a in the 'x 1.4' position the period of the output pulse is 7/5 (= 1.4) times the period of the output waveform with S1a in the divide-by-five

Although there is no shortage of designs for darkroom timers, many of these suffer from the twin drawbacks of a linear timing scale and inconvenient controls that leave the user fumbling about in the dark. The design presented here overcomes these disadvantages by having a logarithmic timing scale and ergonomically designed controls.